전자공학과

주기성을 갖는 입출력 데이터의 연관성 분석을 통한 회귀 모델 학습 방법

센서 데이터는 전류, 전압, 온도 등과 같이 로봇이나 회로와 같은 산업 설비에 내장된 센서로부터 측정되고, 이러한 센서 데이터는 고장이나 결함을 예측하기 위해 활용된다. 분류 모델은 고장 혹은 결함의 종류를 확률 범위로 나뉜 클래스로 예측하지만, 회귀 모델은 무수히 많은 수치 중에 하나의 값을 예측해야 하므로 상대적으로 학습 난이도가 더 높다. 특히 주기성을 갖는 센서 데이터는 동일한 출력을 예측해야 할 때, 입력이 서로 다른 값 갖기 때문에 회귀 모델의 성능이 떨어지게 된다. 본 연구에서는 슬라이딩 윈도우 기법을 이용하여 입력 데이터를 패턴화하여 학습 데이터 셋을 구성하는 방법을 제안한다.

StyleGAN2-ADA

작품 속 인물 특성에 따른 얼굴 생성 웹 개발

사용자에게 작품 제목과 작품 속 인물의 이름을 입력받아 작품 속 인물 특성에 따라 생성한 얼굴 이미지를 제공하는 웹 애플리케이션입니다. 웹 애플리케이션은 플라스크를 기반으로 만들어졌으며 StyleGAN2-ADA를 이용한 특성별 이미지 생성 모델과 face morphing을 결합해 설계했습니다. StyleGAN2-ADA의 precision이 평균 0.663으로 적절한 품질의 이미지를 생성할 수 있음을 확인했고, 인물의 실제 시각화 된 이미지와 인물이 소유한 특성과 그렇지 않은 특성의 LPIPS의 distance를 비교해 보았을 때, 소유한 특성이 약 8.6 % 작아 연결된 특성과 작품 속 인물의 상관관계를 확인할 수 있습니다.

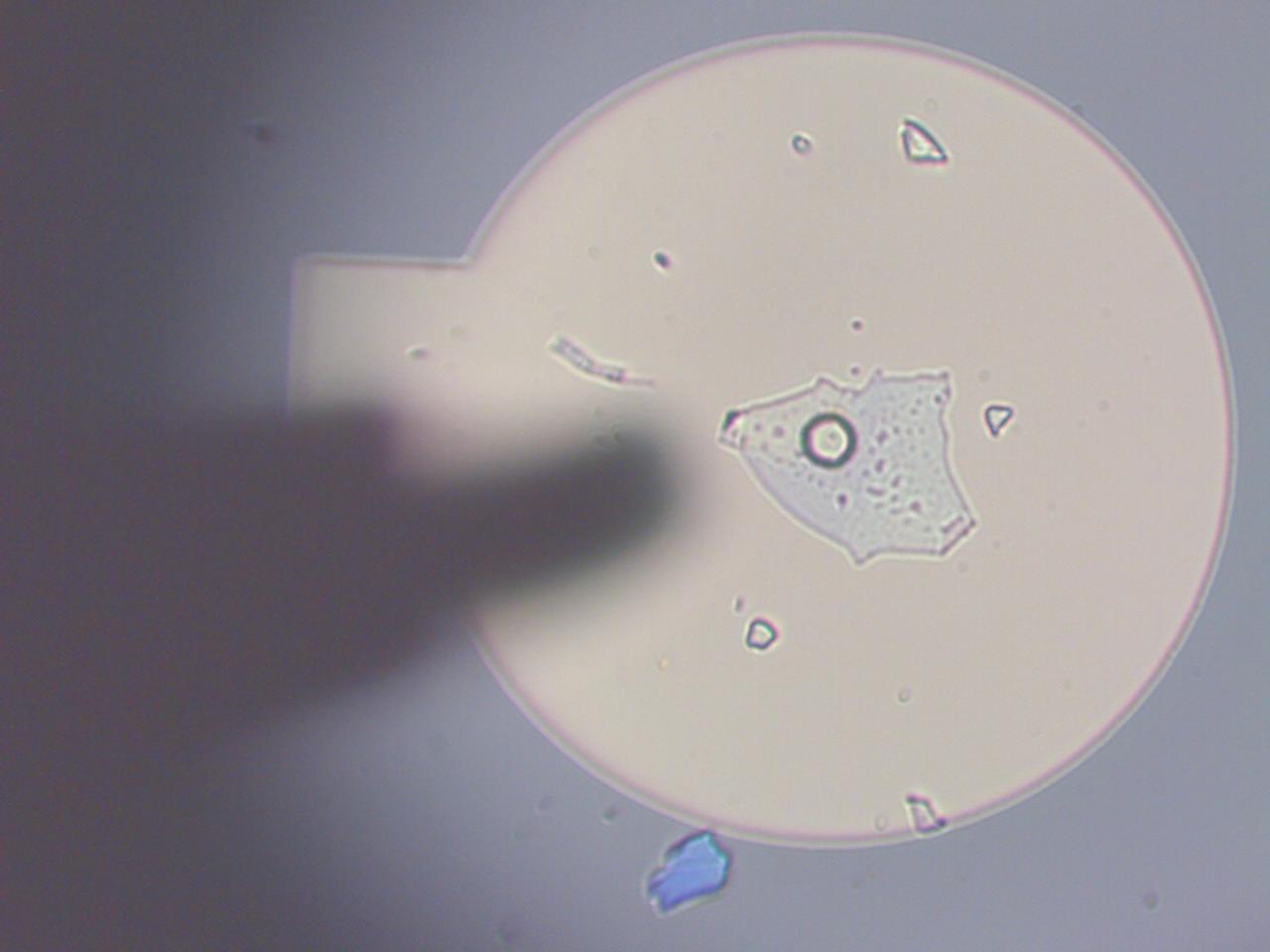

2D material을 활용한 VDWH photodetector

2D material을 사용한 VDWH photodetector입니다. 일반적인 photodetector와 달리 MoS2라는 2d 물질을 이용하였습니다. 전기적인 특성이 우수하기 때문에 기존의 실리콘 등을 대체할 수 있도록 연구가 되고 있는 물질 중 하나입니다. 이 물질을 Ge(저마늄)등의 서로 다른 물질과 접합하게 되면 hetero structure가 형성되고 전자와 정공을 한 곳으로 모으는데 더 용이하게 됩니다. 반도체 공정과 전사를 통해 이를 구현했습니다, 그 후 빛의 파장을 변화시켜가며 전류를 측정하였고, 측정한 전류를 통해 responsivity와 on/off ratio등을 비교할 수 있었습니다.

Double gate Ge/Si Hetrojunction TFET for the Low-Power Application

따라서 TFET 소자를 설계하여 SS과 on/off ratio를 최적화시켜 저전력 동작을 할 수 있는 소자를 설계합니다. 특히 Gate controllability를 증가시키기 위해 Double gate 구조로 설계를 진행하였고, Si TFET과 Ge TFET 간의 trade-off를 해결할 수 있는 Si/Ge hetrojunction 구조로 설계했습니다. 이 구조의 body 두께에 따른 특성이 어떻게 변하며 저전력 소자로 동작할 수 있는 최적의 두께인지 연구했습니다.

이더리움

기존의 주가예측 모델과는 달리 새로운 주가예측 모델 제안

주가에대한 관심이 높아지면서 예측모델에 관한 관심이 증대하였습니다. 시간의 흐름에따라 데이터가 변하는 시계열 데이터가 주가인점을 반영하여 RNN 모델만을 사용하는 것과는 달리 데이터 자체의 feature을 이용하는 모델을 제안하는 바입니다.

Love Inverter

영구자석 동기 전동기(PMSM)의 두가지 제어 기법

현대 산업의 발전과 함께 전동기는 중요한 역할을 담당해왔다. 그 과정에서 전동기 역시 직류전동기, 유도전동기, 전자석 동기전동기 등 기존 전동기의 문제점을 개선하거나 효율을 극대화하기 위한 여러 전동기들이 개발되었다. 그 중에서도 영구자석 동기 전동기는 타 전동기들보다 상대적으로 효율이 높아 특히 전동차의 전동기로써 많이 사용된다. 이러한 영구자석 동기 전동기를 더 효율적으로 사용하기 위해 제어 방법에 따른 특징들을 관찰한다.

잘자요우리애긔

Machine Learning을 이용한 EEG 신호처리에 따른 Hyponogram 예측 모델에 관한 연구

본 연구는 기존의 다양한 데이터를 사용하여 수면의 깊이를 예측하는 모델과 다르게 2-channel의 EEG 데이터를 통해 수면의 깊이를 의미하는 Hyponogram을 예측하는 모델에 관한 연구로, 뇌파의 주파수 대역에 따라 8개의 feature를 생성하여 머신러닝을 진행하였다. 다양한 방법의 신호처리를 진행한 데이터를 Gradient boosting 알고리즘을 사용하여 생성된 모델의 각 Feature importance를 확인하여 각 모델별 예측 결과에 대해 비교, 분석을 진행하여 신호처리 방법에 따른 예측률 차이를 확인하였다.

고인물의 힘

매입형 영구자속전동기(IPMSM)의 직접토크제어(DTC)와 HPF

영구자석이 회전자 내부에 삽입된 매입형 영구 자속 전동기 제어(IPMSM)는 SPMSM보다 유효 공극이 작고 고속운전이 유리하다. IPMSM에는 직접토크제어(DTC)와 FOC(Field Oriendted Control)이 있는데, DTC는 전동기 parameter의 영향이 적어 제어가 비교적 간단하고 연산시간과 응답특성이 빠르다는 장점이 있으므로 DTC 제어를 사용하였다. DTC 제어에서 토크 리플에 따라 지령 속도변화에 따라 d-q축 및 3상 전류에 리플이 크게 발생하므로 이를 제거하기 위해 HPF를 도입하였다.