전자공학과

여상엽

PMIC를 위한 저전력 LDO 설계

에너지 효율적인 LDO를 설계하기 위해서 Adaptive Bias회로를 활용하여 회로의 에너지 효율을 높인다. 하지만 회로에서 소모되는 전류가 줄어들면 transient response 성능이 줄어들어 overshoot/undershoot이 발생할 때 회로가 regulation 되는 시간이 오래걸린다. 이러한 문제점을 feedback cap과 slew enhancer circuit을 적용하여 transition response를 개선하여 settling time을 줄이고, overshoot undershoot 전압을 감소시킨다.

4조

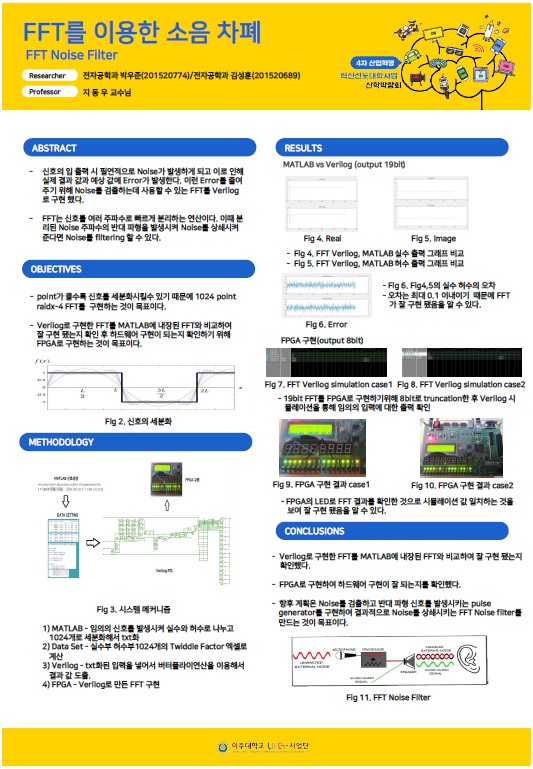

FFT를 이용한 소음 차폐

신호의 입출력시 필연적으로 Noise가 발생하게 되고 이로 인해 실제 결과 값과 예상 값에 Error가 발생한다. 이런 Error를 줄여주기 위해 Noise를 검출하는데 사용할 수 있는 FFT를 Verilog 로 구현했다. FFT는 신호를 여러 주파수로 빠르게 분리하는 연산이다. 이때 분리된 Noise 주파수의 반대 파형을 발생시켜 Noise를 상쇄시켜준다면 Noise를 filtering 할 수 있다.

DCN

딥러닝을 활용한 공지사항 분류 모델 설계

학교 홈페이지에 게시되는 공지사항은 자세한 분류가 되어있지 않은 경우가 많다. 또한 수시로 업데이트되는 공지사항을 확인하는 것이 어렵기 때문에 많은 사용자들이 불편을 호소한다. 따라서 텍스트 마이닝의 특성을 활용하여 공지사항을 효과적으로 확인할 수 있는 공지사항 분류 모델을 설계한다. 제안하는 공지사항 분류 모델은 딥러닝 알고리즘인 DNN을 기반으로 하여 사용자 각각의 선호 기준에 맞게 공지사항을 분류하고, 나아가 웹 페이지로 한정된 공지사항 게시 방법을 확장하여 공지사항의 즉각적인 확인을 도와준다.

스파이

Difference between foot EMG on diabetes

당뇨병이 진행되면 합병증으로 인해 말단 기관 중 하나인 발에 다양한 질환이 발생하게 된다. 특히 혈관이 당 노폐물로 막히게 되어 neuropathy와 연관된 muscle dystrophy가 발생해 파손된다. 그러므로 발의 상태에 따라 당뇨 발의 치료에 대한 시점을 판단하는 것이 중요하나 대다수의 측정 방법이 부정확하거나 불편하다. 따라서 전압차이가 신경보다 더욱 큰 근육의 근전도를 측정하여 질환의 진행상태를 확인하는 것이 보다 용이하다. 본 연구에선 당뇨 진행 상태에 따른 환자들의 근전도 데이터를 기반으로 LSTM 기반 딥 러닝 모델에 학습시켜 당뇨환자의 발 건강 상태를 확인하고 치료시점 판단의 가능성을 확인하였다.

5조

위성 SAR 영상에서 딥러닝을 이용한 선박 검출 연구

위성 SAR 영상을 이용하여 딥러닝을 기반으로 한 선박 검출 모델 설계, 성능 검증 및 평가하였다. CNN 구조로 모델을 구현하였고, 최적화 함수로 Adam optimizer를 사용하였다. 유럽우주국의 Sentinel-1 위성 분석 툴인 SNAP을 이용해 897개의 데이터 셋을 수집하였으며, 그중 'VV, VH, Angle ellipsoid‘ 3가지 데이터를 입력 변수로 사용하였다. 성능 평가에선 MiniBatch Size와 테스트 데이터 개수를 변경하며 정확도를 측정하였고 테스트 데이터 170개, MiniBatch Size 100개에서 최고 정확도 91.76 %인 것을 확인하였다.

융합캡스톤디자인2 9조

자율 주행을 이용한 강화 학습 방식의 비교 연구

저희는 자율주행을 활용하여 강화학습의 방식인 Q-learning의 두 알고리즘을 비교하였습니다.Q-learning의 두 알고리즘인 Q-table과 Q-network는 목적과 환경에 따라 정확도와 효율성이 달라집니다. 이를 가시적으로 비교할 수단이 필요했고 강화학습으로 자율주행 모델링을 형성했을 때, 두 알고리즘에 어떤 차이가 있고 효율적인지를 확인하였습니다. 이를 통해 두 강화학습 방식의 장단점과 차이점, 자율주행을 강화학습으로 모델링 할 때, 어떤 방식이 효율적인지 알 수 있습니다. 또한 본 논문에서 수행된 비교분석을 통해 다양한 강화학습에 대한 비교 연구에 도움이 될 것입니다.

휴머노이드 로봇의 토크 제어에 관한 연구

Position Control 방법을 사용하여 보행을 제어하는 것은 이상적인 상황에서는 잘 동작하지만 외란(Disturbance)에 취약한 단점을 가짐. 이 단점을 보완할 수 있는 Torque Control을 제어 방법으로 선택할 필요성 존재. 따라서 본 연구는 CTM과 RNE를 이용하여 보행을 제어하는 Torque Controller를 설계하고 성능과 강점을 확인.

김재현 교수님 11조

CNN을 활용한 SAR 이미지 선박판별

Synthetic Aperture Radar(SAR) 이미지에서 선박을 판단하고 정확도를 출력하는 Convolutional Neural Network(CNN)모델을 구현했다. 구현된 모델을 이용해 Convolution Layer, Fully Connected Layer, Pooling Layer의 개수에 따른 선별된 선박 이미지의 정확도의 변화를 분석했다.